TUGAS FLIP-FLOP

1. Master-Slave Flip Flop

Master-Slave JK Flip-flop disusun dari SR Flip flop

Sebuah Master Slave JK Flip-flop dibentuk dari 2 buah RS flipflop, dimana operasi dari kedua RS flip-flop dilakukan secara bergantian dengan memberikan input yang berlawanan pada kedua RS flip-flop. Prinsip dasarnya jika clock diberi input 1 gerbang AND 1 dan 2 akan aktif, Master akan menerima data yang dimasukan melalui input J dan K sementara gerbang AND 3 dan 4 tidak aktif, hasil outputnya=0, sehingga Slave tidak ada respon(kondisi tidak berubah). Dan jika clock diberi output 0, gerbang 3 dan 4 aktif, Slave akan mengeluarkan output di Q dan Q’, master tidak merespon input, karena gerbang AND 1 dan 2 tidak aktif.

Master-Slave JK Flip-flop disusun dari SR Flip flop

Skema Master-Slave

IC yang digunakan pada rangkaiyan MASTER SLAVE

1. 7476 JK flip-flop dual =>

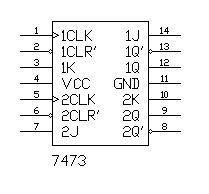

2. 7473 JK flip-flop dual =>

4. 4027 Master slave J-K flip-flop dengan picu sisi naik, Pre dan Clr tak sinkron dan keluaran Q dan Q’

=>

2. Mengapa hasil dari RS Flip-Flop dengan Clock selalu berbeda hasilnya pada saat di reset ?...

Keluaran Q pada RS flip-flop tidak dapat segera merespon masukan S dan R sebelum ada masukan clock.

Kondisi respon RS flip-flop terlihat sama seperti kondisi respon tanpa klok, bedanya keluaran hanya merespon masukan S dan R setelah terjadi klok =1. Dalam hal ini Q bertindak sebagai 1bit di dalam memori. Yang menyebabkan nilai akhir bisa berubah-ubah karena s=1, r=1 tidak boleh diset serentak yang menghasilkan output yang tidak konsisten. Oleh karna itu mengapa RS Flip-Flop hasilnya berbeda saat di reset.

Tidak ada komentar:

Posting Komentar